# IMPLEMENTATION OF A CARTESIAN GRID INCOMPRESSIBLE NAVIER-STOKES SOLVER ON MULTI-GPU DESKTOP PLATFORMS USING CUDA

by Julien C. Thibault

A thesis

submitted in partial fulfillment of the requirements for the degree of Master of Science in Computer Science Boise State University

April 2009

© 2009 Julien C. Thibault ALL RIGHTS RESERVED

## APPROVAL TO SUBMIT THESIS

This thesis presented by Julien C. Thibault entitled Implementation of a Cartesian Grid Incompressible Navier-Stokes Solver on Multi-GPU Desktop Platforms Using CUDA is hereby approved:

> Inanc Senocak Advisor

Date

Amit Jain Committee Member Date

Timothy Barth Committee Member Date

John R. Pelton Dean of the Graduate College Date

Dedicated to my parents

## ACKNOWLEDGMENTS

Many thanks to Drs. Massimiliano Fatica, Patrick Legresley, David Luebke from NVIDIA and Timothy J. Barth from NASA Ames Research Center for helpful discussions on CUDA and GPU computing. Thanks are extended to Marty Lukes and Luke Hindman of Boise State University for their help with building our desktop supercomputers.

I would like to thank Dr Amit Jain for allowing me to join the Master program in Computer Science at Boise State University. He has always been there to advise me, through my first semester when I was only an exchange student, and later on when I decided to join the program.

I thank Dr Inanc Senocak for his support all along this thesis. He made this experience really valuable for me. The subject of this thesis was challenging not only because of the parallel architecture of the GPUs but also because of the numerical methods involved. He helped me understand the challenges of computational fluid dynamics, in which I had only basic knowledge, to allow me to implement the software solution.

Many thanks to Boise State University and to the College of Engineering for the financial aid they provided and their ongoing support during these two last years. Finally I thank NVIDIA Corporation and Micron Technology, Inc. for their hardware donations. This work was partially funded by NASA Idaho EPSCoR Research Initiation grant.

### ABSTRACT

Today's Graphics Processor Units (GPU) are powerful computation platforms used not only for graphic rendering but also for multi-purpose computation. Now reaching a teraflops of peak performance and over a 100 GB/sec of bandwidth, GPUs outperform the latest CPUs and provide a new high-performance computing platform. New languages such as CUDA and Brook+ allow developers to target the programmable unit of the GPUs without a graphics programming background. Scientists and engineers in various fields have started benefiting from the last generations of GPUs. In this thesis, the implementation of a Navier-Stokes solver for incompressible flow around urban-like domains is presented. Transport and dispersion of contaminants in urban environments is an area of intense research. The computational fluid dynamic (CFD) models necessary to provide realistic simulations require heavy computation, usually only possible on CPU clusters. This thesis presents the base for an urban dispersion model implementation on desktop platforms, using one or multiple GPUs as coprocessors. The governing equations implemented for this thesis are common to many problems in CFD where flow motion is involved. Using a single Tesla C870 GPU card, the CUDA implementation of the lid-driven cavity problem runs 33 times faster than a serial C code running on a single core of an AMD Opteron 2.4GHz processor. A speedup of 100 was reached by associating the Tesla S870 quad-GPU system to a quad-core CPU machine. Computations for both GPU and CPU are single precision. A more complex application including obstacle capability was developed to model building effects in the domain. Using the quad-GPU system, the flow-field in a domain of 1.28 km  $\times$  1.28 km  $\times$  320 m was computed. A low Reynolds number flow-field projection of 22 minutes (1000 time steps) could be simulated in 3 minutes. Results show that an urban dispersion is feasible on this type of platform and that models can be run within minutes to provide emergency responses. More generally, it shows that complex CFD problems can benefit from multi-GPU desktop architectures.

## TABLE OF CONTENTS

| ABSTRACT vi |                    |            |                                                               |  |  |  |  |

|-------------|--------------------|------------|---------------------------------------------------------------|--|--|--|--|

| LI          | LIST OF TABLES xii |            |                                                               |  |  |  |  |

| LI          | ST (               | OF FIC     | GURES                                                         |  |  |  |  |

| LI          | ST (               | OF AB      | BREVIATIONS xix                                               |  |  |  |  |

| 1           | INT                | rodu       | UCTION 1                                                      |  |  |  |  |

|             | 1.1                | Proble     | em Context 1                                                  |  |  |  |  |

|             | 1.2                | Thesis     | Statement 4                                                   |  |  |  |  |

|             |                    | 1.2.1      | Objectives                                                    |  |  |  |  |

|             |                    | 1.2.2      | Procedures 6                                                  |  |  |  |  |

|             | 1.3                | Prior Work |                                                               |  |  |  |  |

|             |                    | 1.3.1      | GPGPU computing 8                                             |  |  |  |  |

|             |                    | 1.3.2      | Contaminant Transport and Dispersion in Urban Environments 10 |  |  |  |  |

| <b>2</b>    | TE                 | CHNIC      | CAL BACKGROUND 13                                             |  |  |  |  |

|             | 2.1                | GPGF       | PU As a Solution                                              |  |  |  |  |

|             |                    | 2.1.1      | Evolution of the Graphics Pipeline 13                         |  |  |  |  |

|             |                    | 2.1.2      | CUDA Hardware Architecture                                    |  |  |  |  |

|             |                    | 2.1.3      | CUDA Programming Model 16                                     |  |  |  |  |

|             |                    | 2.1.4      | Compilation and Development Tools 18                          |  |  |  |  |

|   | 2.2 | Gover | ning Equations                                        | 19 |

|---|-----|-------|-------------------------------------------------------|----|

|   |     | 2.2.1 | Wave Equation                                         | 19 |

|   |     | 2.2.2 | Governing Equations of Incompressible Fluid Flows     | 20 |

|   |     | 2.2.3 | Turbulence Modeling                                   | 20 |

|   | 2.3 | Nume  | rical Methods                                         | 22 |

|   |     | 2.3.1 | Wave equation                                         | 22 |

|   |     | 2.3.2 | Incompressible Navier-Stokes Equations                | 22 |

|   |     | 2.3.3 | Turbulence Modeling                                   | 24 |

| 3 | GP  | U IMF | PLEMENTATION & VALIDATION                             | 26 |

|   | 3.1 | Imple | mentation of the Wave Equation                        | 26 |

|   |     | 3.1.1 | Wave Propagation Problem                              | 26 |

|   |     | 3.1.2 | Main code (Host-side)                                 | 27 |

|   |     | 3.1.3 | Single-GPU Implementation                             | 27 |

|   |     | 3.1.4 | Dual-GPU Implementation                               | 29 |

|   | 3.2 | Imple | mentation of a 3D Incompressible Navier-Stokes Solver | 30 |

|   |     | 3.2.1 | Lid-Driven Cavity Problem                             | 30 |

|   |     | 3.2.2 | Single-GPU Implementation                             | 31 |

|   |     | 3.2.3 | Multi-GPU Implementation                              | 41 |

|   |     | 3.2.4 | GPU Shared Memory Implementation                      | 45 |

|   |     | 3.2.5 | Validation                                            | 47 |

|   | 3.3 | Comp  | lex Geometry Capability                               | 48 |

|   |     | 3.3.1 | Additional Features                                   | 48 |

|   |     | 3.3.2 | Obstacle Logic                                        | 49 |

|   |     | 3.3.3 | Main Code                                             | 54 |

|              |     | 3.3.4  | Multi-GPU Implementation                            | 54 |

|--------------|-----|--------|-----------------------------------------------------|----|

|              |     | 3.3.5  | Final Output                                        | 56 |

| 4            | CO  | MPUI   | TATIONAL PERFORMANCE ANALYSIS                       | 60 |

|              | 4.1 | 2D W   | Tave Equation                                       | 60 |

|              | 4.2 | Incom  | pressible Navier-Stokes Solver                      | 62 |

|              |     | 4.2.1  | Serial CPU Code Benchmarking                        | 62 |

|              |     | 4.2.2  | Kernel acceleration using the shared memory         | 65 |

|              |     | 4.2.3  | GPU speedup relative to CPU                         | 67 |

|              |     | 4.2.4  | Multi-GPU Scaling Analysis                          | 68 |

|              | 4.3 | Comp   | elex Geometry Capability Implementation             | 71 |

|              |     | 4.3.1  | Impact of Thread Block Configuration                | 71 |

|              |     | 4.3.2  | Weight of Data Transfer in Multi-GPU Implementation | 73 |

|              |     | 4.3.3  | Register Usage                                      | 75 |

|              |     | 4.3.4  | Speedup Analysis                                    | 76 |

| 5            | CO  | NCLU   | SIONS                                               | 78 |

|              | 5.1 | Result | ts                                                  | 78 |

|              | 5.2 | Furth  | er Work                                             | 80 |

| R            | EFE | RENC   | ES                                                  | 82 |

| $\mathbf{A}$ | HIC | GH PE  | <b>CRFORMANCE COMPUTING INFRASTRUCTURE</b>          | 87 |

|              | A.1 | GPU    | Hardware Specifications                             | 87 |

|              | A.2 | Hardy  | vare Bandwidth Tests                                | 88 |

| в            | DIS | SCREI  | TIZATION OF THE GOVERNING EQUATIONS                 | 90 |

|   | B.1 | Contir | nuity Equation                                      | 90  |

|---|-----|--------|-----------------------------------------------------|-----|

|   | B.2 | Navier | -Stokes Equations                                   | 90  |

|   |     | B.2.1  | General Form of the Navier-Stokes Equations         | 90  |

|   |     | B.2.2  | Discretization of the Advection and Diffusion Terms | 91  |

|   | B.3 | Strain | Rate Tensor                                         | 94  |

| С | CU  | DA co  | de                                                  | 95  |

|   | C.1 | Param  | eter Definition                                     | 95  |

|   | C.2 | Memo   | ry Indexing                                         | 96  |

|   | C.3 | Mome   | ntum                                                | 97  |

|   |     | C.3.1  | Global Memory Implementation                        | 97  |

|   |     | C.3.2  | Shared Memory Implementation                        | 98  |

|   | C.4 | Diverg | gence                                               | 99  |

|   | C.5 | Pressu | re                                                  | 99  |

|   |     | C.5.1  | Pressure constant                                   | 99  |

|   |     | C.5.2  | Global Memory Implementation                        | 99  |

|   |     | C.5.3  | Shared Memory Implementation                        | 99  |

|   | C.6 | Veloci | ty Correction                                       | 100 |

## LIST OF TABLES

| 4.1 | GFLOPS performance of the serial CPU version of our CFD code                         |    |

|-----|--------------------------------------------------------------------------------------|----|

|     | and NPB benchmark codes on two different computers (Intel Core                       |    |

|     | 2 Duo (E8400) 3.0 GHz and AMD Opteron (8216) 2.4 GHz). $LU$                          |    |

|     | factorizes an equation into lower and upper triangular systems. The                  |    |

|     | iteration loop of $MG$ consists of the multigrid V-cycle operation and               |    |

|     | the residual calculation. $S\!P$ is a simulated CFD application. Our CFD             |    |

|     | code simulates a lid-driven cavity problem.                                          | 63 |

| 4.2 | Kernel execution times for different block configurations. The urban-                |    |

|     | like domain was represented by a $256 \times 256 \times 64$ grid and each simulation |    |

|     | ran for 200 time steps                                                               | 72 |

| 4.3 | Execution time of the different kernels and data exchange in a quad-                 |    |

|     | GPU simulation. An urban-like domain was represented by a 256 $\times$               |    |

|     | $256 \times 64$ grid and each simulation ran for 1000 time steps                     | 74 |

| 4.4 | Register usage (single and multi-GPU implementations)                                | 75 |

| A.1 | Bandwidth tests for memory transfers between host and device                         | 89 |

## LIST OF FIGURES

| 1.1 | Performance comparison between Intel CPUs and NVIDIA GPUs (cour-              |    |

|-----|-------------------------------------------------------------------------------|----|

|     | tesy of NVIDIA).                                                              | 2  |

| 1.2 | CFD Simulation of plume dispersion in Time Square, New York (cour-            |    |

|     | tesy of Patnaik et al. [41])                                                  | 5  |

| 2.1 | Processing steps for graphics rendering (courtesy of NVIDIA)                  | 14 |

| 2.2 | The CUDA Model (courtesy of NVIDIA). In this example, the CUDA                |    |

|     | grid is composed of $3 \times 2$ blocks, each containing $5 \times 3$ threads | 16 |

| 2.3 | Staggered Grid. Pressure $P$ is located in the cell centers. $u$ and $v$      |    |

|     | components of the velocity are located respectively in the midpoints of       |    |

|     | the vertical and horizontal edges                                             | 23 |

| 3.1 | Wave simulation on a $1024\times1024$ domain with different initial condi-    |    |

|     | tions and boundary conditions                                                 | 26 |

| 3.2 | Host-side code for the CUDA implementation of the wave equation.              |    |

|     | The wave kernel is launched at each time step for synchronization             |    |

|     | across CUDA blocks.                                                           | 28 |

| 3.3 | Assignment of a subdomain of $4\times 4$ to a CUDA block. Threads work        |    |

|     | on the inner cells but need extra data to represent the borders of the        |    |

|     | subdomain (ghost cells)                                                       | 28 |

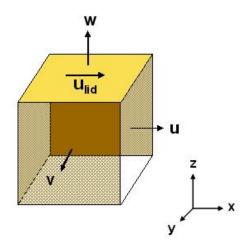

- 3.4 A schematic of the physical domain for the lid-driven cavity problem. No-slip conditions are applied on the YZ planes in the east and west directions and on the bottom XY plane in the south direction. Free-slip (symmetry) condition is applied to the front and back XZ planes. A constant velocity is applied on the XY plane in north direction. The velocity component in the x-direction is set to a constant  $U_{lid}$  value... 31

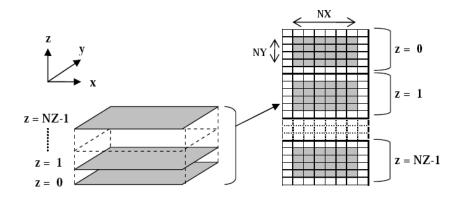

- 3.5 Mapping of a 3D computational domain to a 2D matrix. The mapping is used on both the CPU and the GPU sides. Cells in white on the 2D matrix represent the ghost (halo) cells to apply the boundary conditions. 32

- 3.6 Example of index logic to map a 2D CUDA block decomposition onto

a 3D domain. The 3D domain (a) is represented in a 2D-way (b). A

2D CUDA grid is then mapped onto the 2D domain (c). (d) represents

the thread indices associated to the CUDA block decomposition. . . . . 33

- 3.7 Final index logic to map the CUDA block decomposition onto a 3D domain. (a) An 8 × 4 × 4 domain is stored as a 1D array in memory.

(b) A 2D CUDA grid is mapped onto the 1D array in memory, each 2 × 2 thread block working on two levels in the z-direction...... 35

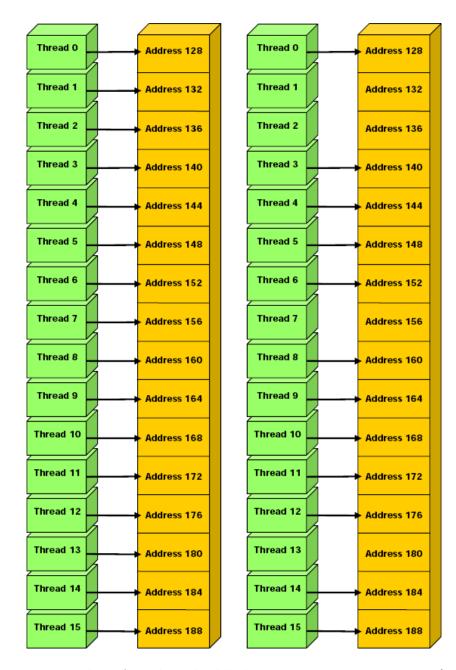

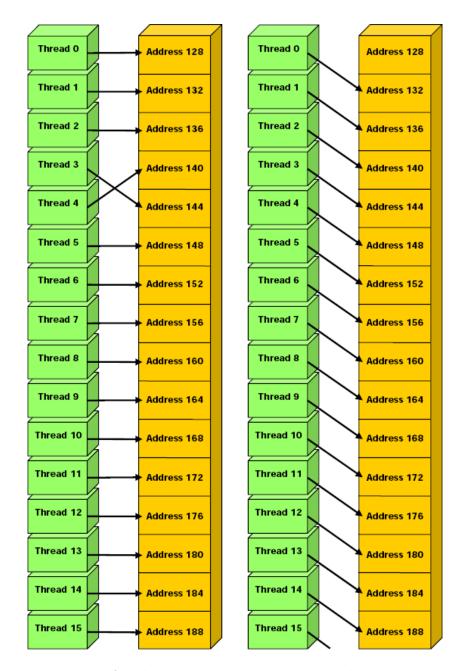

- 3.10 Examples of global memory access by devices with compute capability

1.2 and higher (courtesy of NVIDIA). Left: random float memory

access within a 64B segment, resulting in one memory transaction.

Center: misaligned float memory access, resulting in one transaction.

Right: misaligned float memory access, resulting in two transactions.

40

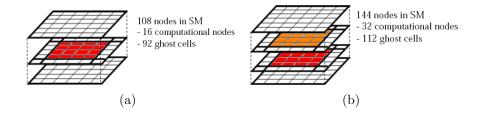

| 3.14 | Two different approaches for shared memory usage in a $4 \times 4$ block               |    |

|------|----------------------------------------------------------------------------------------|----|

|      | configuration. Colored cells are updated by the threads while the                      |    |

|      | white cells are only used as data source (ghost cells). Each cell center               |    |

|      | represents a computational node. a) Each thread updates one cell only                  |    |

|      | (red cells). b) Each thread works on 2 cells in the same vertical column.              |    |

|      | Cells in red are updated during the first iteration and orange ones in                 |    |

|      | the second iteration.                                                                  | 45 |

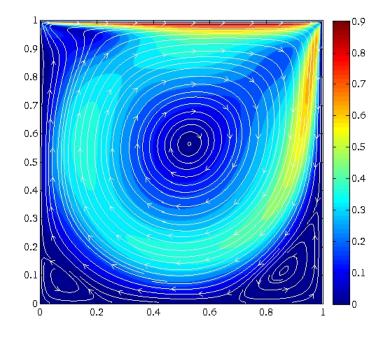

| 3.15 | Distribution of velocity magnitude and streamlines at steady-state for                 |    |

|      | Re=1000. Low velocity regions are represented in dark blue while high                  |    |

|      | velocity regions are represented in red                                                | 47 |

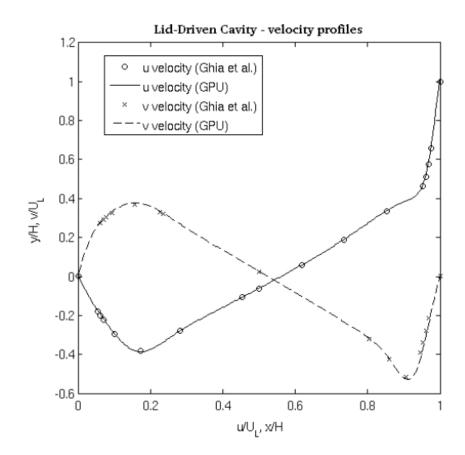

| 3.16 | Validation of the GPU code results with benchmark data given in                        |    |

|      | Reference [23]. Both $u$ and $v$ components of the velocity field are                  |    |

|      | shown.                                                                                 | 48 |

| 3.17 | Flag matrix used to represent the obstacles at the pressure points. The                |    |

|      | gray cells (1's) represent a building                                                  | 49 |

| 3.18 | Obstacle logic applied to the U-component of the velocity in the $XZ$                  |    |

|      | plane                                                                                  | 52 |

| 3.19 | host-side code used for the obstacle logic                                             | 54 |

| 3.20 | Partial host-side code to calculate flow field with 3D obstacles                       | 55 |

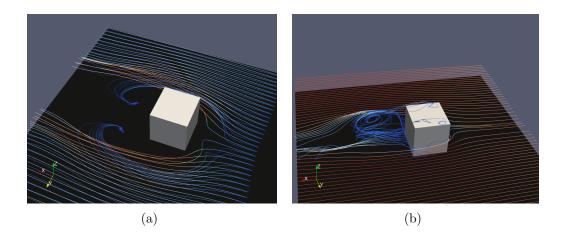

| 3.21 | Flow around a surface-mounted cube for a turbulent regime ( $Re$ =                     |    |

|      | 1000). Grid size is $256 \times 128 \times 64$ . Red streamlines represent high        |    |

|      | velocity magnitudes while blue streamlines represent lower velocity                    |    |

|      | magnitudes                                                                             | 56 |

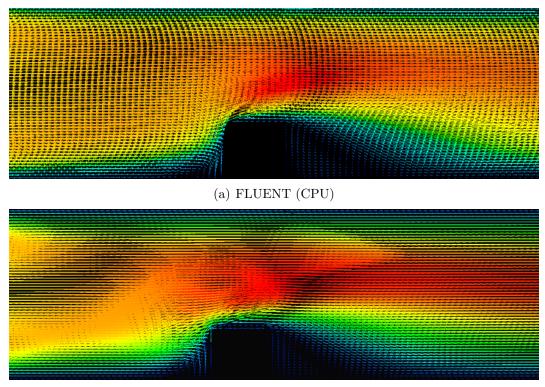

| 3.22 | FLUENT (CPU) and CUDA (GPU) simulations for a laminar flow                             |    |

|      | around a surface-mounted cube ( $Re = 42$ ). Grid size is $256 \times 128 \times 64$ . | 57 |

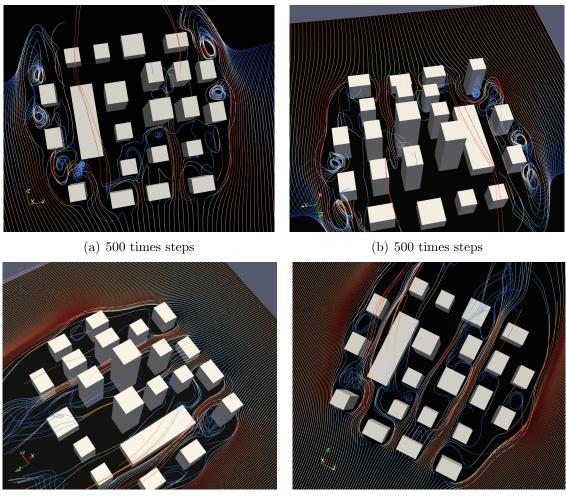

| 3.23 | Low Reynolds number flow in an urban-like domain $(Re = 155)$ .                     |    |

|------|-------------------------------------------------------------------------------------|----|

|      | Execution times are relative to the quad-GPU platform running a                     |    |

|      | simulation using $256 \times 256 \times 64$ computational nodes and representing a  |    |

|      | domain of 1.28 km $\times$ 1.28 km $\times$ 320 m. Red streamlines represent high   |    |

|      | velocity magnitudes while blue streamlines represent lower velocity                 |    |

|      | magnitudes                                                                          | 58 |

| 3.24 | Simulation of a domain of 1.28 km $\times$ 1.28 km $\times$ 320 m on a 256 $\times$ |    |

|      | $256 \times 64$ grid using a second-order Adams-Bashfort scheme. The                |    |

|      | Reynolds number for these simulations is $Re = 155$ and 1000 times                  |    |

|      | steps represent over 10 minutes of physical time                                    | 59 |

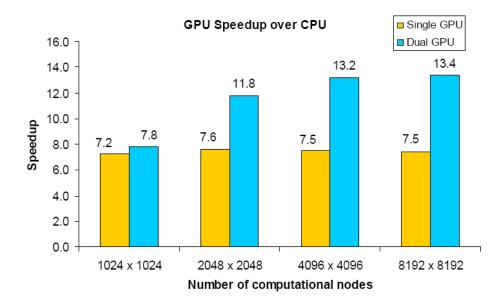

| 4.1  | Acceleration of the wave simulation. GPU speedup relative to a serial               |    |

| 4.1  |                                                                                     |    |

|      | CPU implementation is plotted for different physical domain sizes. The              |    |

|      | single GPU solution gives constant speedup over the serial code while               |    |

|      | the dual-GPU results indicate speedup for sufficiently large problems               | 60 |

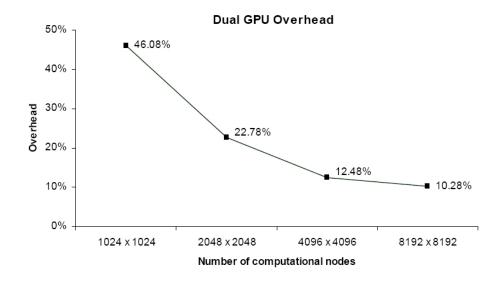

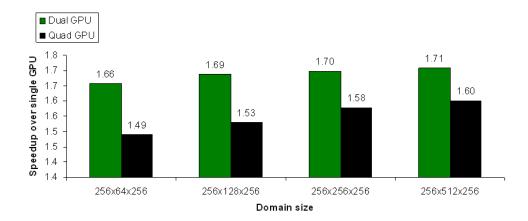

| 4.2  | Overhead of the dual GPU implementation over the single GPU im-                     |    |

|      | plementation.                                                                       | 61 |

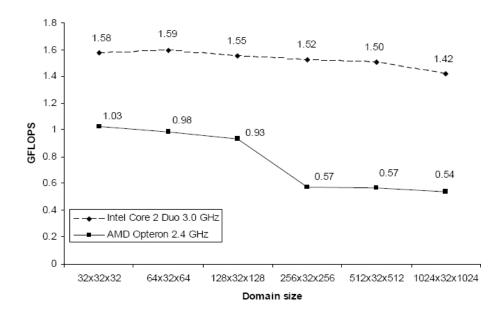

| 4.3  | GFLOPS performance of the serial (CPU) in-house developed CFD                       |    |

|      | code with increasing domain sizes.                                                  | 64 |

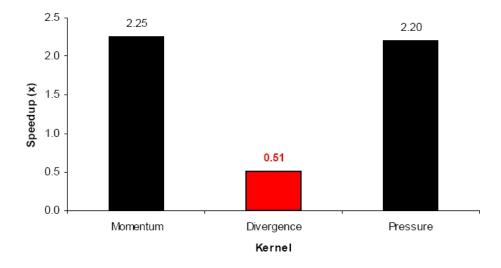

| 4.4  | Kernel speedup of shared memory implementation relative to a full                   |    |

|      | global memory implementation (domain size is $256 \times 32 \times 256$ ). Tests    |    |

|      | showed that the momentum and pressure kernels benefit from a shared                 |    |

|      | memory implementation, giving a speedup of more than $2\times$ relative a           |    |

|      | kernel implementation that uses only the global memory                              | 65 |

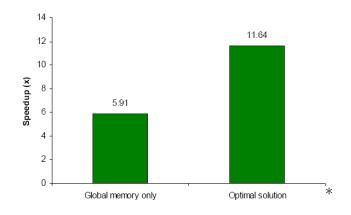

| 4.5  | GPU speedup relative to the serial (CPU) code for global memory-only             |    |

|------|----------------------------------------------------------------------------------|----|

|      | and optimized versions (domain size is $256 \times 32 \times 256$ ). The optimal |    |

|      | solution uses shared memory for the momentum and pressure kernels                |    |

|      | while the other kernels use global memory only                                   | 66 |

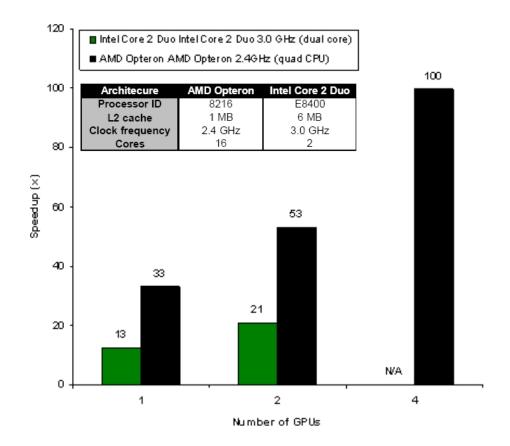

| 4.6  | GPU speedup over serial CPU code for a domain of $1024\times32\times1024$        |    |

|      | computational nodes. Quad-GPU results are not available for the Intel            |    |

|      | Core 2 Duo configuration because no quad-GPU/dual Intel Core 2 Duo               |    |

|      | platform was available for this study                                            | 67 |

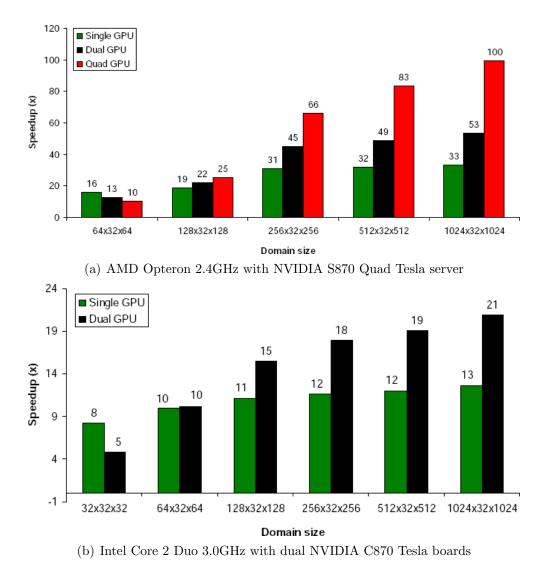

| 4.7  | Single and multi-GPU speedup relative to a single CPU core                       | 69 |

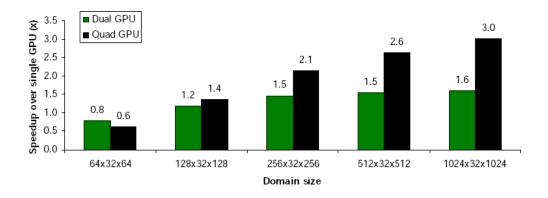

| 4.8  | Multi-GPU scaling on the S870 server with dual-CPU platform. The                 |    |

|      | multi-GPU platform does not scale well when then there is not a one              |    |

|      | CPU core per GPU ratio                                                           | 70 |

| 4.9  | Multi-GPU scaling on the S870 server with quad-CPU platform. As                  |    |

|      | the problem size increases the multi-GPU solutions scale better                  | 71 |

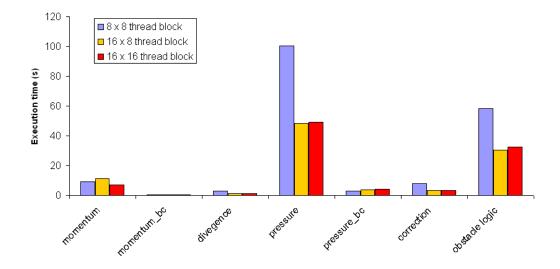

| 4.10 | Comparison of kernel execution times for different block configurations.         |    |

|      | The urban-like domain was represented by a $256\times256\times64$ grid and       |    |

|      | each simulation ran for 200 time steps.                                          | 72 |

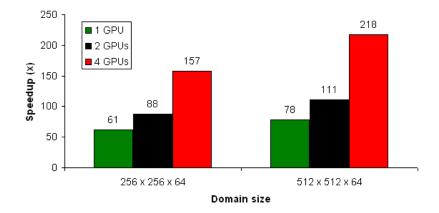

| 4.11 | Single and multi-GPU speedup relative to a single CPU core of an                 |    |

|      | AMD Opteron 2.4 GHz for urban simulations                                        | 76 |

| A.1  | GPU computing hardware utilized in the research. One of the com-                 |    |

|      | puters is equipped of 2 Tesla C870 (a), a second one is equipped with            |    |

|      |                                                                                  |    |

|      |                                                                                  | 88 |

| A.1  |                                                                                  | 10 |

|      | server (c)                                                                       | 88 |

## LIST OF ABBREVIATIONS

- **API** Application Programming Interface

- $\mathbf{CB}-\mathbf{Chemical}\text{-Biological}$

- **CFD** Computational Fluid Dynamics

- $\mathbf{CPU}$  Central Processing Units

- **CUDA** Compute Unified Device Architecture

- FLOPS Floating-point Operations Per Seconds

- $\mathbf{GPGPU}$  General Purpose GPU

- **GPU** Graphics Processor Units

- **HPC** High Performance Computing

- ${\bf LBM}-{\rm Lattice}\text{-}{\rm Boltzman}\ {\rm Method}$

- LES Large Eddy Simulation

- MPI Message Passing Interface

- **PDE** Partial Differential Equations

- ${\bf SDK}$  Software Development Kit

- **SIMD** Single Instruction Multiple Data

## CHAPTER 1

## INTRODUCTION

### **1.1** Problem Context

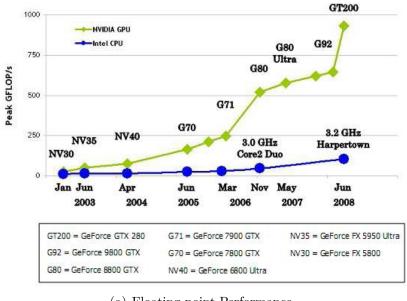

In the last decade, CPU designers have focused on developing multi-core architectures instead of increasing the clock frequency by putting more transistors on the die because of power constraints [29]. GPU designers have adopted the many-core strategy early on, because graphics rendering is a parallel task. GPUs are based on the stream processing architecture that is suitable for compute-intensive parallel tasks [38, 40]. Modern GPUs can provide memory bandwidth and floating-point performances that are orders of magnitude faster than a standard CPU. Figure 1.1 depicts the growing gap in peak performance between GPU and CPU over the last five years. Currently, NVIDIA GPUs outperform Intel CPUs on floating point performance (Figure 1.1(a)) and memory bandwidth (Figure 1.1(b)), both by a factor of roughly ten [38]. Until recently, using the GPUs for general purpose computation was a complicated exercise. A good knowledge of graphics programming was required, because GPU's old fixed-function pipeline did not allow complex operations [39]. GPUs have evolved into a programmable engine, supported by new programming models trying to find the right balance between low access to the hardware and high-level programmability [39]. The *BrookGPU* programming model, released in 2004 by Stanford University, offered one of the first development platforms for gen-

(a) Floating-point Performance

Figure 1.1: Performance comparison between Intel CPUs and NVIDIA GPUs (courtesy of NVIDIA).

(b) Memory Bandwidth

eral purpose GPU (GPGPU) programming [10, 40]. BrookGPU provides a GPU abstraction layer that enables data parallelism. It keeps the programmer away from having an extensive knowledge of graphics programming - like OpenGL - while being platform independent. In 2007, NVIDIA released a new programming model for its own line of GPUs: Compute Unified Device Architecture (CUDA) [38]. With CUDA, NVIDIA offers a common architecture and programming model for its own line of The C-based application programming interface (API) of CUDA enables GPUs. data parallelism through the use of shared memory, but also computation parallelism thanks to the introduction of the thread and grid concepts. The CUDA programming model has found success in the GPGPU community. There is also a recent effort called MCUDA [46] to program multi-core CPU architectures with the same paradigms exposed in CUDA. On the other hand, AMD offers a compute abstraction layer (CAL) for GPU programming. A modified version of the Brook open source compiler (Brook+) was developed to support this cross-platform interface to the GPU. Both AMD CAL and Brook+ are available in AMD's software development kit (SDK) [30].

Advances in many-core architectures have been tremendous, but using the full potential of many-core architectures is not an easy task. Engineers and scientists may need to rewrite and optimize their legacy sequential codes to harness the computepower of modern day multi-core CPUs, and many-core GPUs. Message Passing Interface (MPI) programming [21] has been widely adopted in parallel scientific computations. The framework provides a high level API that allows programmers to transparently make use of multiple processors on both shared and distributed systems. The programmer does not have to deal with the details of the communication protocol between the nodes. On shared memory systems, POSIX multithreading offers low level functions to implement multi-threaded systems, while OpenMP provides a certain abstraction layer [12], which makes it more accessible to software developers. In contrast, CUDA offers a different approach that specifically targets the many-cores on a single GPU. It is the programmer's responsibility to optimize the usage of the memory and the threads available on the streaming cores [42]. Multi-GPU parallelism is not currently addressed by CUDA, which means that implementation for multiple GPUs is explicitly performed by programmers. External tools such as OpenMP, MPI or POSIX can be associated to CUDA in order to benefit from a GPU cluster or a multi-GPU desktop platform. In the future, parallel projects like CUDASA [47] might provide new frameworks that will ease development on multi-GPU systems.

#### **1.2** Thesis Statement

#### 1.2.1 Objectives

The current set of computational models that is adopted by the emergency responders to simulate chemical-biological (CB) contaminant dispersion is based on simplified empirical models [27]. The predictive capability of these models is often unsatisfactory, but they are still being employed because of their relatively fast run-times. The *Joint Effect Model* (JEM), funded by the Department of Defense, establishes a key performance parameter (KPP). According to the KPP, urban dispersion models with advanced features turned off shall provide hazard prediction and graphical display within 10 minutes. Many current CFD applications are not able to deliver a solution within that time frame, even when the physics modeling features are turned off [44]. During this research the main objective was to develop an incompressible 3-D Navier-Stokes solver to compute wind fields in urban-like domains. This work serves as a baseline implementation towards a CFD-based urban dispersion model.

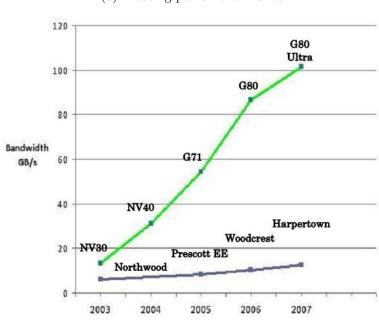

Figure 1.2: CFD Simulation of plume dispersion in Time Square, New York (courtesy of Patnaik et al. [41])

It also provides a novel obstacle capability to simulate the effects of the buildings on the flow field and a subgridscale turbulence model for large-eddy simulations (LES) of turbulent flows. The NVIDIA CUDA technology was chosen to implement the discretized form of the governing equations on CUDA-capable GPU architecture. The goal was to substantially shorten turn-around time for simulations on a multi-CPU / multi-GPU desktop computer. The CFD code that was developed as part of this thesis solves a generic set of partial differential equations for incompressible fluid dynamics (Navier-Stokes equations). Broadly speaking, the computational techniques and algorithms that were developed for multi-CPU/multi-GPU architectures as part of this research can be extended to different thermo-fluid applications such as aerodynamic flows or weather forecasting.

#### 1.2.2 Procedures

In order to develop the proposed CFD code, a step-by-step development approach was followed. This allowed rigorous accuracy tests of the numerical implementations. The following tasks were accomplished as part of the research:

- Implementation of the 2D wave equation to get familiar with the CUDA paradigms and apply them to a CFD problem on multi-GPU platforms.

- Implementation of a 3D Navier-Stokes solver which is the core of the final CFD code. The code was validated with the laminar channel flow exact solution and lid-driven cavity benchmark simulation [49]

- Implementation of a 3D Navier-Stokes solver with novel obstacle capability (to mimic building effects) [50].

- Implementation of a Smagorinsky large-eddy simulation turbulence model for wind-field modeling in realistic urban environments

In a parallel effort, a serial C code was developed to validate the logic of the new features added at each step of the development. It was also used as a benchmark for speedup analysis. The following high performance computing (HPC) platforms with different GPU-CPU configurations were available to perform speedup and multi-GPU scaling analysis:

• "hellboy.boisestate.edu"- dual-GPU / dual-core CPU machine

$2 \times \text{NVIDIA}$  Tesla C870 boards ( $2 \times 128$  processors)

3.0 GHz Intel Core 2 Duo E8400 CPU (1333 MHz front side bus)4GB DDR2 800 MHz memory

• "barth.boisestate.edu"- quad-GPU / 16-core CPU machine

$1 \times \text{NVIDIA S870 Server} (4 \times 128 \text{ processors})$

$8 \times$  Dual-core 2.4 GHz AMD Opteron 8216 CPU (1000 MHz front side bus)

16GB DDR2 667 MHz memory

• "sawtooth.boisestate.edu"- quad-GPU / dual-core CPU machine

$2 \times \text{NVIDIA}$  GeForce 9800 GX2 boards ( $2 \times 256$  processors)

3.0 GHz Intel Core 2 Duo E8400 CPU (1333 MHz front side bus)

4GB DDR3 1333 MHz memory

These three computing platforms offered different CPU and GPU configurations. First, the speedup provided by a single GPU over a serial code was determined for different types of CPU. But mainly, it helped analyzing the effects of the CPU and the GPU hardware on multiple-GPU (2, 3 or 4 GPUs) platform performance. The Appendix A.1 gives more details about the GPU computing hardware that was utilized in this research. The implementation of these different tasks and the analysis of the results using the GPU computing infrastructure is presented in the following sections of this paper.

### 1.3 Prior Work

#### 1.3.1 GPGPU computing

Prior to the introduction of the CUDA and Brook programming models, several Navier-Stokes solvers have been implemented for the GPU. Harris [26] implemented a 3D solver to create a physically-based cloud simulation using the Cq programming language from NVIDIA. It is a high-level programming language for graphics on GPUs, which operates as a layer above OpenGL. His implementation was based on the "stable fluids" method proposed by Stam [45]. This method is adapted to graphics application because of the real-time visualization constraint. In Reference [33] the Navier-Stokes equations are solved for flow around complex geometries following the work of Harris [26]. Due to its relative potential for easy parallelization, the Lattice-Boltzman method (LBM) has also been implemented in different studies addressing complex geometries. In Reference [31], GPU implementation of LBM resulted in speedup of  $15 \times$  relative to the CPU implementation. In Reference [17], an LBM was implemented on a GPU cluster to calculate winds and contaminant dispersion in urban areas. A speedup of  $4.6 \times$  relative to a CPU cluster was achieved in their study [17], which demonstrates that GPU clusters can serve as an efficient platform for scientific computing.

High performance parallel computing with CUDA has already attracted various scientists in several disciplines, such as molecular dynamics [3,32,52], computational biology [43], linear algebra [6,11], weather forecasting [34] and artificial intelligence [7]. In the computational fluid dynamics (CFD) field, Tolke and Krafczyk [51] implemented a 3D Lattice-Boltzman method for flow through a generic porous medium. They obtained a gain of up to two orders of magnitude with respect to the computational of an Intel Xeon 3.4GHz. Brandvik and Pullan [9] mapped 2D and 3D Euler solvers to the GPU using BrookGPU and CUDA programming models. For the CUDA version of the 3D Euler solver, their computations on NVIDIA 8800GTX showed a speedup of 16 relative to a single core of an Intel Core 2 Duo 2.33GHz, whereas the BrookGPU implementation of the 3D Euler solver showed a modest speedup of only 3 on the ATI 1950XT. Molemaker et al. [35] developed a multi-grid method to solve the pressure Poisson equation. The CUDA implementation of the multi-grid pressure Poisson solver produced a speedup of 55 relative to a 2.2MHz AMD Opteron processor [35]. Recently, Elsen et al. [16] showed that complex scientific simulations are feasible on GPUs. They implemented a BrookGPU version of the compressible Euler equations in order to simulate hypersonic vehicles. Compared to a single core of an Intel Core 2 Duo 2.4GHz the GPU implementation achieved speedups ranging from 15 to 40.

The recent literature attests to the compute-potential of GPU computing with new programming models. Numerous studies have adopted the CUDA programming model to numerical problems that have practical applications in engineering and science at large [36]. Currently, most of the current GPU applications utilize single-GPU platforms. The potential of GPU clusters has already been demonstrated [17]. But the current motherboards can now host multiple GPUs and become the core of a *superdesktop* computer for a relatively cheap cost. This thesis introduces the implementation of a CFD code on multi-GPU/multi-CPU desktop platforms and demonstrates the potential of such platforms.

#### 1.3.2 Contaminant Transport and Dispersion in Urban Environments

Urban dispersion is a scientific field that projects how contaminant plume spreads through urban environments. It is usually associated with chemical-biological (CB) contaminant release (accidental release or terrorist attack) although it was traditionally used for preventive purposes like air pollution warning. Until recently the computational hardware did not allow scientists to run fast-response urban dispersion simulations based on CFD models. Instead, fast-running empirical or semi-empirical models were used to obtain running times acceptable for emergency responses. With the latest advances in high-performance computing hardware, CFD models can now be run on machines delivering teraflops of computing performance. They might provide a new alternative to semi-empirical building resolved (SEB) models. A typical urban CFD domain is usually only a couple square kilometers large, between  $1 \text{ km}^2$ and  $5 \text{ km}^2$ , with a vertical dimension less than 1 km. The grid system resolution is usually between 1 m and 5 m. The urban environment is modeled using 3-D building data, usually extracted from an existing database. Several studies [1,2,15,19] showed that models need to be evaluated against field data. A single-building simulation [15] is a first step to evaluate the accuracy of a model but larger-scale domains are necessary to validate the model with realistic environments. The Oklahoma [2] and Manhattan field experiments [1] provide the necessary data to evaluate models in existing urban areas. In 2003 the Department of Homeland Security sponsored a field experiment in Oklahoma City, the Joint Urban 2003 Atmospheric Dispersion Study [2]. The study covered the central business district of the city, a domain of 900 m by 1200 m. It included around 40 city blocks and 150 buildings. Although a cluster of 50 m tall buildings was part of the domain, most of these buildings were under 10 m. Tracer releases were performed on a month period, including day-time and nighttime releases. Several types of sensors (crane, sonic anemometers) were used to measure 5 or 10 minute averaged tracer concentrations. The study showed that the few tall buildings actually had a big impact on the overall plume dispersion.

The *MID05* experiment included six days of tracer and meteorological exper-The studied area was located in midtown Manhattan (south of Central iments. Park). It covered a domain of 2 km by 2 km including deep street canyons with buildings reaching 150 meters and only a couple meters apart from each other. Thirtyminute averaged tracer concentrations were collected by 64 different outdoor samplers. Since the results of these field experiments were published, several studies have been conducted to evaluate the accuracy of urban dispersion models. The Joint Urban 2003 data were used in [20] and [28] to evaluate a Reynolds-averaged Navier-Stokes solver CFD model and a semi-empirical building resolved model, respectively. Results showed that after customizing the models, the simulated dispersions were comparable to the observed tracer releases. In [19], six different models were evaluated against the data from the MID05 experiment. This study showed that in a real emergency context, where no update on the models is possible, the different models do not perform well and results may vary a lot from a model to another. Flaherty et al. [19] pointed that in order to reach high-accuracy simulations, the input data for the simulations must include accurate building data (databases) and accurate atmospheric data. This means that the studied area should be equipped with enough sensors to build an accurate state of the dispersion. Previous experiments on the area should also prescribe boundary conditions if the sensors cannot provide enough data.

There is still a great need for improvement in urban dispersion modeling. Patnaik et al. [41] showed that realistic urban contaminant dispersion is feasible. Figure 1.2

describes how plume dispersion can be visualized with their FAST-3D-CT model [41]. On the other hand those simulations and the postprocessing steps are still very expensive. Currently emergency responders cannot afford this type of simulation. Urban CFD simulations can be accelerated significantly if the numerical methods are carefully implemented [24, 25]. Advances in computing hardware can further accelerate computations, and allow advanced modeling features that were too timeconsuming for fast-running simulations. An urban dispersion model based on a second-order accuracy LBM was developed for a 32-node GPU cluster by Fan et al. [17]. They simulated the dispersion of airborne contaminants in the Times Square area of New York City. The simulation covered an area of around 1.16 km  $\times$  1.13 km, including 91 blocks and around 850 buildings. This domain was represented by a grid of  $480 \times 400 \times 80$  computational nodes, resulting in a resolution of 3.8 m. Results showed a speedup of  $4.6 \times$  over the CPU cluster implementation. This is very promising as GPU hardware greatly improved since this study was conducted in 2004. Their work represents the first implementation of the LBM on a GPU cluster. The LBM is very popular today as it is fairly easy to parallelize. This thesis present the first CFD-based implementation of the incompressible Navier-Stokes equations on multi-GPU desktop platforms using CUDA.

## CHAPTER 2

## TECHNICAL BACKGROUND

## 2.1 GPGPU As a Solution

#### 2.1.1 Evolution of the Graphics Pipeline

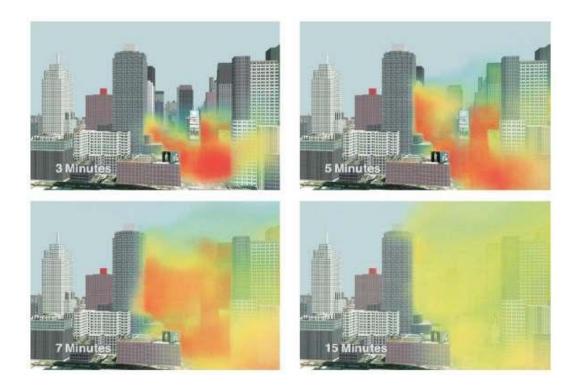

Originally built for graphics rendering, GPUs are now powerful programmable engines, suitable for general purpose computation [39]. In this section, the main stages of the graphics pipeline will be introduced and the evolution of the GPU architecture will be briefly described. The graphics pipeline can be divided into 5 main stages [40]:

- Vertex processing: The different input objects are formed from individual vertices and made part of the scene system through scaling and shading (interaction with the lights). This stage is adapted to parallelization as each vertex can be computed independently.

- Primitive assembly: The vertices are collected and assembled into triangles.

- Rasterization: This stages determines which pixels are going to be hidden from the camera point-of-view. Each triangle is filled with a "fragment" which represents the actual pixels that are displayed at the screen-space location.

- Fragment operations: The final color of each fragment is determined by combining the pixel's attribute (color, depth, position) with textures fetched from

the memory. This stage is very demanding but each fragment can be computed in parallel.

• Composition: Fragments are assembled into the final image, keeping only one color per pixel.

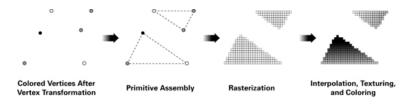

Figure 2.1 describes the different processing steps that are needed to translate the input vertices into the final pixel data. The first generations of GPUs were imple-

Figure 2.1: Processing steps for graphics rendering (courtesy of NVIDIA)

mented with a fixed-function pipeline. But the demand for more complex lighting and shading effects required some modifications on the pipeline to allow user-defined functions for vertex and fragment operations. Consequently, vertex and fragment programs, in addition to a larger limit on their size, gained more features to render more complex effects. The unified Shader Model 4.0, now supported by NVIDIA's and AMD's GPUs, defines the different features the vertex and fragments should support. This includes dynamic flow control (branches, loops) and 32-bit integers and 32-bit floating-point numbers. On one hand GPU designers built increasingly parallel sets of pipelines to compute vertices and fragments faster. On the other hand the programmable hardware unit of the pipeline became more and more complex and eventually became common to the fragment and vertex programs. The GPU architecture is now adapted to high-performance general computation as data-parallelism is conserved and programmers only have to target a single hardware unit which supports the functions they can expect from a CPU.

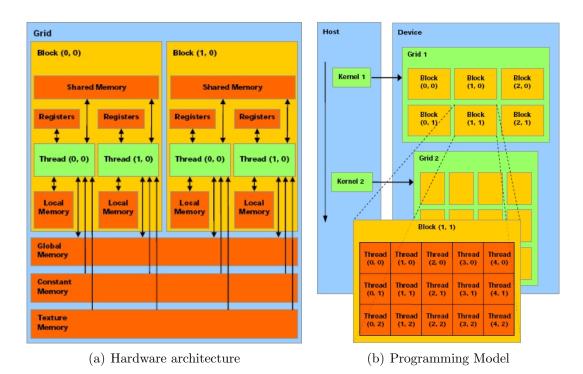

#### 2.1.2 CUDA Hardware Architecture

In GPU designs, transistors are devoted to data processing rather than data caching and flow control [38]. A GPU is an example of a Single Instruction, Multiple Data (SIMD) multiprocessor. In the CUDA programming model, compute-intensive tasks of an application are grouped into an instruction set and passed on to the GPU such that each thread core works on different data but executes the same instruction. The CUDA memory hierarchy does not really differ from the one for a conventional multiprocessor. Closer to the core, the local registers allow fast ALU operations. The shared memory, seen by all the cores of a single multiprocessor, can be compared to a first-level cache (L1), as it provides a memory closer to the processors that will be used to store data that tend to be used over time by any core [38]. The difference in CUDA is that the programmer is responsible for the management of this "GPU cache". The last level in this hierarchy is the global memory, the RAM of the device. It can be accessed by any processor of the GPU, but for a higher latency cost. Threads can actually perform simultaneous scatter or simultaneous gather operations if those addresses are aligned in memory [38]. Coalesced memory access is crucial for superior kernel performance as it hides the latency of the global memory. The challenge for a CUDA software developer is then, not only the parallelization of the code, but also the optimization of the memory accesses by making the best use of the shared memory and the coalesced access to the global (device) memory. Each multiprocessor also has read-only constant cache and texture cache. The constant cache can be used by the threads of a multiprocessor when trying to read the same constant value at

Figure 2.2: The CUDA Model (courtesy of NVIDIA). In this example, the CUDA grid is composed of  $3 \times 2$  blocks, each containing  $5 \times 3$  threads.

the same time. Texture cache on the other hand is optimized for 2D spatial locality and should be preferred over global device memory when coalesced read cannot be achieved [38].

#### 2.1.3 CUDA Programming Model

The computation core of the CUDA programming model is the kernel, which is passed on to the GPU and executed by all the processor units, using different data streams. Figure 2.2(b) presents the layout of the threads in the CUDA programming model. Each kernel is launched from the host side (CPU), and it is mapped to a thread grid on the GPU. Each grid is composed of thread blocks. All the threads from a particular block have access to the same shared memory and can synchronize together. On the other hand, threads from different blocks cannot synchronize and can exchange data only through the global (device) memory [38]. A single block can only contain a limited number of threads, depending on the device model. But different blocks can be executed in parallel. Blocks executing the same kernel are batched together into a grid. Blocks are managed by CUDA and executed in parallel in a batch mode. The programmer needs to define the number of threads per block and the grid size (number of blocks) before launching the kernel. As mentioned earlier, CUDA API is an extension to the C programming language. It provides functions to manage the computations on the GPU. The full list of functions is discussed in detail in the CUDA programming guide [38]. The major functions used in this study are cudaMalloc() and cudaMemcpy() functions. These functions allocate memory on the GPU and copy data from the CPU memory into the device memory of the GPU, respectively. The cudaFree() function is used to free memory on the device. The kernel is launched by specifying the size of the grid (number of blocks) and the size of the blocks (number of threads) using the following prototype: kernelName<<gridSize, blockSize>>(). \_\_synchthreads() can be used inside a kernel to synchronize all the threads of a same block. Global synchronization is not addressed by the CUDA model. A practical way to force a global synchronization is to exit the kernel before launching a new one. In addition, the CUDA API introduces the qualifiers \_shared\_, \_device\_ and \_constant\_ to define the type of memory a variable should use. The function qualifiers \_device\_, \_global\_, and \_host\_ specify whether the GPU or the CPU should execute and call the qualified function [38].

### 2.1.4 Compilation and Development Tools

### **CUDA** Toolkit

The CUDA Toolkit [36] enables CUDA applications to run on a general purpose computer with Windows, Linux or Mac operating systems, using the GPU as a coprocessor to the CPU. Jobs are launched on the GPU from the host process using remote procedure calls, supported by the CUDA toolkit.

### NVCC compiler

Nvcc [37] is used to compile CUDA code, which is a combination of C/C++ code for the host side and GPU code for the device. The host code can actually be compiled with any general purpose C/C++ compiler that is available on the host platform such as the GNU C compiler gcc [22], while the device code uses proprietary NVIDIA compilers and assemblers. Compilation options for the host code are then similar to a general purpose compiler, but NVCC offers more options to specify the mode of CUDA compilation, such as the release, emulation or fat device code binaries modes.

### CUDA Software Development Kit (SDK)

The SDK [36] offers the necessary libraries and configuration files to build a CUDA application. Several applications are available for demonstration purpose and code source. The SDK 1.1 was used to build the applications developed during this research.

### **CUDA** profiler

The SDK [37] also offers a profiler. It can output different statistics about the CUDA program that is executed against it. The profiler provides information about GPU time, CPU time, the number of coalesced access memory and branch conditions, which can be displayed in summary tables but also in various kinds of plots. The CUDA profiler is useful to identify kernel implementations that have a high number of non-coalesced stores/loads and warp serializations (branch conditions).

## 2.2 Governing Equations

Before describing the CUDA implementation of the CFD code, it is necessary to introduce the governing equations. They are defined in the following sections along with the numerical methods that allow their implementation.

### 2.2.1 Wave Equation

The wave equation is a computationally tractable partial differential equation (PDE) that can serve as a model to learn and experiment with the CUDA programming model before targeting more complex PDEs such as the Navier-Stokes equations. The two dimensional wave equation is defined as:

$$\frac{\partial u^2}{\partial^2 t} = c^2 \nabla^2 u \tag{2.1}$$

where u is the amplitude of the wave and c the propagation speed of the wave.

### 2.2.2 Governing Equations of Incompressible Fluid Flows

### **Continuity Equation**

The continuity equation Eq. 2.2 describes the conservation of mass:

$$\frac{\partial u}{\partial x} + \frac{\partial v}{\partial y} + \frac{\partial w}{\partial z} = 0 \tag{2.2}$$

where u, v and w are the components of the velocity vector in the x, y and z directions, respectively.

### **Navier-Stokes Equations**

The Navier-Stokes equations, along with the continuity equation (Eq. 2.2), describe the motion of incompressible viscous fluids:

$$\frac{\partial \mathbf{u}}{\partial t} + \mathbf{u}\nabla \cdot \mathbf{u} = -\frac{1}{\rho}\nabla P + \nu\nabla^2 \mathbf{u} + \nabla \cdot \bar{\bar{\boldsymbol{\tau}}}^R$$

(2.3)

where **u** is the velocity vector, P is the pressure,  $\rho$  is the density,  $\bar{\tau}^R$  is the subgrid scale Reynolds stress term, and  $\nu$  is the kinematic viscosity. Under laminar flow conditions the Reynolds stresses are absent from Eq. 2.3. For turbulent flow conditions, a turbulent eddy viscosity needs to be defined. In the Reynolds-averaged Navier-Stokes approach u, v, w, and P represent ensemble-averaged quantities and in the large-eddy-simulation approach u, v, w, and P represent filtered quantities [48].

### 2.2.3 Turbulence Modeling

The present research effort mainly focused on laminar flow simulations. Additionally, an LES subgrid scale model for turbulent flows was implemented, which will be validated in future. The Large Eddy Simulation (LES) approach is used for the turbulence closure problem. In LES modeling, large scale energetic flow structures are resolved by the computations, while the effect of unresolved small-scale flow structures are represented by a sub-grid scale (SGS) model. The presented implementation uses the Smagorinsky eddy viscosity model [48]. The Smagorinsky model is characterized by a mixing-length  $l_{mix}$  which is proportional to the filter width is defined as:

$$l_{mix} = C_s \Delta, \tag{2.4}$$

where  $C_s$  is the Smagorinsky constant ( $C_s \approx 0.1$ ) and  $\Delta$  is the characteristic width of the filter. In the present study, a box filter is implemented, in which case:

$$\Delta = \sqrt[3]{\Delta x \Delta y \Delta z},\tag{2.5}$$

where  $\Delta x$ ,  $\Delta y$  and  $\Delta z$  are the grid resolutions in the x, y, z directions, respectively. The mixing-length appears in the eddy viscosity as follows

$$\nu_t = l_{mix}^2 \sqrt{S_{ij} S_{ji}},\tag{2.6}$$

where the strain rate tensor  $S_{ij}$  is given by:

$$S_{ij} = \frac{1}{2} \left( \frac{\partial u_i}{\partial x_j} + \frac{\partial u_j}{\partial x_i} \right)$$

(2.7)

# 2.3 Numerical Methods

### 2.3.1 Wave equation

Second order accurate numerical schemes in both time and space are used to discretize the wave equation. The discretized form of the equation can be written as follows

$$u_{i,j}^{t+1} = c \left(1 - 2\rho^2\right) u_{i,j}^t + \rho^2 \left(u_{i+1,j}^t + u_{i-1,j}^t + u_{i,j+1}^t + u_{i,j-1}^t\right) - u_{i,j}^{t-1}$$

(2.8)

where u is the amplitude of the wave, and i, j, and t are the indices for the x-direction, y-direction and the time level, respectively.  $\rho$  defines the ratio of time step to the spatial resolution  $(\Delta t/\Delta h)$ . The wave propagation speed c has a value of 1.0. The wave equation is discretized on a spatial domain size of  $[0, \pi; 0, \pi]$ .

### 2.3.2 Incompressible Navier-Stokes Equations

### Staggered Grid

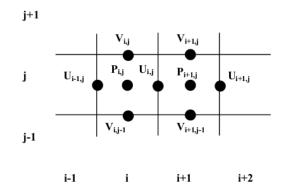

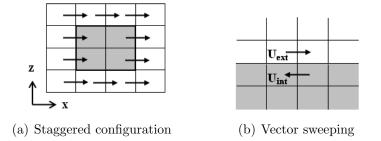

The Navier-Stokes equations can be discretized on either a staggered or a nonstaggered (collocated) grid. The staggered grid eliminates the odd-even pressure oscillations that may occur on non-staggered grids [48]. A staggered configuration is used for this implementation. Figure 2.3 shows the location of the computational nodes for each component (u, v, w) of the velocity field and the pressure P on a staggered grid.

### **Projection Algorithm**

Second-order accurate central difference scheme is used to discretize the advection and diffusion terms of the Navier-Stokes equations on a uniform staggered grid [18].

Figure 2.3: Staggered Grid. Pressure P is located in the cell centers. u and v components of the velocity are located respectively in the midpoints of the vertical and horizontal edges.

Both first-order accurate, explicit Euler scheme and second-order accurate Adams-Bashfort were used for the time derivative term. The projection algorithm [14] is then adopted to find a numerical solution to the Navier-Stokes equation for incompressible fluid flows. In the projection algorithm, the velocity field  $\mathbf{u}^*$  is predicted using the momentum equations without the pressure gradient term [14, 18]. The predicted velocity, using a first order Euler scheme, can be written as follows:

$$\mathbf{u}^* = \mathbf{u}^t + \Delta t \left( -\mathbf{u}^t \nabla . \mathbf{u}^t + \nu \nabla^2 \mathbf{u}^t \right), \qquad (2.9)$$

where the index t and  $\Delta t$  represents the time level and time step size, respectively.  $\mathbf{u}^t \nabla \cdot \mathbf{u}^t$  represents the advective term and  $\nu \nabla^2 \mathbf{u}^t$  represents the diffusion term. The discretization of these terms is given in Appendix B.2. A second-order accurate method in space and time is preferable to reduce numerical errors. The second order Adams-Bashfort scheme gives

$$\mathbf{u}^* = \mathbf{u}^t + \Delta t \left[ 1.5 \left( -\mathbf{u}^t \nabla . \mathbf{u}^t + \nu \nabla^2 \mathbf{u}^t \right) - 0.5 \left( -\mathbf{u}^t \nabla . \mathbf{u}^t + \nu \nabla^2 \mathbf{u}^t \right) \right]$$

(2.10)

The discretization for the diffusive and advective terms remains the same (see Appendix B.2) but now the predicted velocity at (t + 1) depends on the diffusive and advective terms at both t and (t - 1).

The predicted velocity field  $\mathbf{u}^*$  does not satisfy the divergence free condition because the pressure gradient term is not included in Eq. 2.9. By enforcing the divergence free condition on the velocity field at time (t + 1), the following pressure Poisson equation can be derived from the momentum equations given in Eq. 2.3:

$$\nabla^2 P^{t+1} = \frac{\rho}{\Delta t} \nabla . \mathbf{u}^* \tag{2.11}$$

In the present study, the above equation is solved using a Jacobi iterative solver to time march the equations to a steady-state solution. A more efficient solver (e.g., geometric multi-grid method) should be adopted for time-accurate unsteady simulations. The pressure field at time (t + 1) is then used to correct the predicted velocity field  $\mathbf{u}^*$  as follows:

$$\mathbf{u}^{t+1} = \mathbf{u}^* - \frac{\Delta t}{\rho} \nabla P^{t+1} \tag{2.12}$$

### 2.3.3 Turbulence Modeling

#### Smagorinsky Subgrid Model

The eddy viscosity  $\nu_t$  defined by Eq. 2.6 is calculated at the pressure point. For the magnitude of the strain rate tensor defined in Eq. 2.6 the discretization given in Appendix B.3 is used. The viscosity is calculated at the pressure point while the viscous terms are evaluated at the cell sides when computing the predicted velocity. A spatial interpolation is then necessary.

### Pressure Poisson Solver

The Jacobi solver implemented in this study is not sufficient for turbulence modeling. Conservation of mass and momentum needs to be be strictly enforced as turbulent models are very sensitive to numerical errors. This can be achieved by using a multigrid method on top of the Jacobi solver.

# CHAPTER 3

# **GPU IMPLEMENTATION & VALIDATION**

# 3.1 Implementation of the Wave Equation

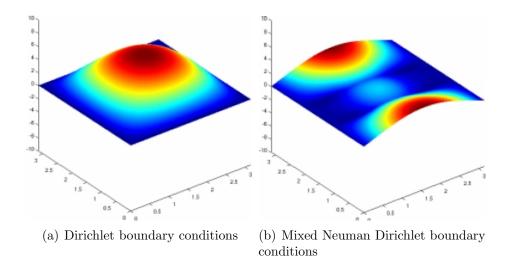

### 3.1.1 Wave Propagation Problem

Figure 3.1: Wave simulation on a  $1024\times1024$  domain with different initial conditions and boundary conditions.

The 2D wave equation is a fairly simple partial differential equation (PDE) to implement. But at the implementation level, the wave equation shares certain common features with other PDEs (time-dependent solution, necessity to apply boundary conditions, etc.). Figure 3.1 shows two different waves obtained from simulations with  $1024 \times 1024$  computational nodes. The first plot is from a simulation with Dirichlet

boundary conditions on all sides (u = 0), while the second plot uses mixed Dirichlet and Neumann boundary conditions.

### 3.1.2 Main code (Host-side)

The discretized form of the wave equation (Eq. 2.8) shows that the computation of a node value at the time level (t + 1) requires information about the same node for the two previous time levels (t and t - 1) and information about the four neighboring nodes from the current time level (t). Therefore, it is necessary to have two matrices to keep track of the last two time levels and another matrix to store the computation results. The next time step starts after each node is computed. At this stage, the matrices are swapped so that the oldest one can be reused to store the result of the next iteration. The matrix representing the time level t now represents the time level (t-1), and the one that stores the results of the previous iteration represents the time level t. This process is repeated at each time steps. Note that costly data transfer between the device and the host is avoided by employing pointers. Figure 3.2 shows how the matrices are swapped at the end of each time step (uold, u, unew representing  $u^{t-1}$ ,  $u^t$  and  $u^{t+1}$ , respectively).

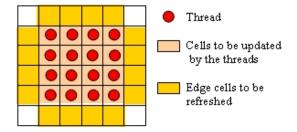

### 3.1.3 Single-GPU Implementation

The computational domain for the wave equation is first decomposed with a checkerboard approach. Each sub-domain is assigned to a particular CUDA block by copying the corresponding data to the shared memory. It includes the subdomain inner cells but also the cells representing the neighboring cells. Figure 3.3 shows an example for a  $4 \times 4$  thread block for simplicity purposes. Only  $4 \times 4$  cells are computed by the threads

```

//for each time step

for (t=0; t < ntstep; t++)

{

//call kernel to compute ut

wave << grid, block >> (unew, u, uold)

//rotate matrices

utemp = uold; uold=u; u=unew; unew=utemp

}

```

Figure 3.2: Host-side code for the CUDA implementation of the wave equation. The wave kernel is launched at each time step for synchronization across CUDA blocks.

but  $6 \times 6$  cells are actually needed to be able to compute the inner cells on the north, south, east and west edges. Note that in the actual implementation, each block holds  $16 \times 16$  threads, for a total of 256 threads per block for faster computations. CUDA actually allows 512 threads per block but the CUDA user guide advises to use 256 threads, which was confirmed in the results of this study. The grid size depends on the size of the physical problem. This first implementation assumes a square domain that can be divided into several  $16 \times 16$  subdomains. A  $1024 \times 1024$  domain for example would contain  $64 \times 64$  blocks. A CUDA block is not a physical multi-processor, the

Figure 3.3: Assignment of a subdomain of  $4 \times 4$  to a CUDA block. Threads work on the inner cells but need extra data to represent the borders of the subdomain (ghost cells).

user can have multiple sub-domains per multi-processor, CUDA takes care of this

step automatically. However, one of the consequences of this feature is that there is no global synchronization of threads from different blocks. This is a performance issue for numerical methods that requires time marching. One needs to synchronize threads after each time step to make sure that the ghost cells are updated. One way to address the issue is to use a multi-pass approach, where a kernel is launched at every time step. This introduces an overhead due to kernel load and, for a shared memory implementation, an overhead due to data transfer between the shared and the global memory. Each block needs to copy its subdomain from the global memory to the shared memory before computation and from the shared memory to the global memory after computation. This last step is required as shared memory data is lost when a new kernel is launched. An alternative approach is to update the ghost cells only every N iteration using a pyramidal approach as explained in [13]. This method reduces the multi-pass approach overhead by having the blocks working on overlapping data. Tests showed that his approach could offer a maximum speedup of  $6.5 \times$  when compared with a Pentium 4 CPU for a 2D problem [13]. This might be acceptable but the quantity of overlapping data for a 3D application would make it unpractical for large 3D problems [13]. Additionally, it implies that the updated status of the domain is needed only every N iterations. Despite the overhead due to kernel load and memory transfer at every time step, the multi-pass recipe seems more appropriate than a pyramidal approach as the final application presented in this thesis is a large 3D simulation problem.

### 3.1.4 Dual-GPU Implementation

As mentioned earlier, CUDA does not provide any API to handle multiple GPUs. The multi- GPU implementation presented here uses POSIX multi-threading. Advanced frameworks like MPI could have been used but POSIX threading assures that the communication overhead of the dual GPU implementation is minimized. OpenMP [12] is also an option with extra features for general parallel computing on shared memory platforms. In the present implementation, the parallelization strategy needs to handle thread operations such as *synchronize*, *create* and *kill*, for which it suffices to use POSIX multi-threading. In dual-GPU implementation, the kernel is almost the same as the one used for the single-GPU implementation. On the other hand, the host code needs to be modified to handle the domain decomposition and multi-threading. Each GPU is responsible for half of the domain (horizontal stripe). One CPU thread is assigned to each GPU. First, it initializes the memory on its device, and then iterate through the time steps by launching the kernel as many times as necessary. After each iteration, the two GPUs need to exchange ghost cells at the domain decomposition boundary. The CPU threads synchronize using a barrier once the edge cells are copied from the device to the host memory. The device memory is then updated and a new iteration starts.

# 3.2 Implementation of a 3D Incompressible Navier-Stokes Solver

### 3.2.1 Lid-Driven Cavity Problem

The lid-driven cavity problem described in Figure 3.4 is a well-established benchmark case in the CFD field [23] and can be used as a validation case to check the correct implementation of the Navier-Stokes equations, because there is no net mass and momentum transport across the domain. The lid-driven cavity is a cubic container filled with a fluid. Its lid moves at constant velocity  $U_{lid}$  (Figure 3.4) and drives the

Figure 3.4: A schematic of the physical domain for the lid-driven cavity problem. No-slip conditions are applied on the YZ planes in the east and west directions and on the bottom XY plane in the south direction. Free-slip (symmetry) condition is applied to the front and back XZ planes. A constant velocity is applied on the XY plane in north direction. The velocity component in the x-direction is set to a constant  $U_{lid}$  value.

fluid inside the container. The flow is assumed to be laminar in this problem. The viscosity is then considered constant and the first-order Euler scheme (Eq. 2.9) is used for time integration. The Reynolds number for this problem is  $Re = U_{lid} \times L/\nu$ , where  $\nu$  is the viscosity of the fluid and L is the height of the cube.

### 3.2.2 Single-GPU Implementation

### **Domain Decomposition and Thread Assignment**

Let NX, NY and NZ be the number of computational nodes in the x, y and z directions for a flow domain, respectively. The 3D domain of size  $NX \times NY \times NZ$  is represented by a 2D matrix of width NX and height  $NY \times NZ$  on the host side, as shown in Figure 3.5. On the GPU side, the same representation is used to store data in global memory. This 2D mapping translates to efficient data transfer between the

host (CPU) and the device (GPU). Note that several matrices are needed to represent the pressure and velocity components at different time levels. Memory allocation on the device is done only once before starting the time stepping. Figure 3.6 gives the

Figure 3.5: Mapping of a 3D computational domain to a 2D matrix. The mapping is used on both the CPU and the GPU sides. Cells in white on the 2D matrix represent the ghost (halo) cells to apply the boundary conditions.

logic used to access data from the GPU. In this example a 2D CUDA grid of  $4 \times 4$  blocks is mapped onto a 3D domain of  $8 \times 4 \times 2$ . Each block is a set of  $2 \times 2$  threads, each thread being mapped to a cell of the domain. The 3D domain is actually represented by a 1D array in the device memory. The corresponding indices of each domain cell are given in Figure 3.6(a) and 3.6(b). The translation from 3D to 1D is defined by:

$$A[i + j \times NX + k \times NX \times NY] = B[k][j][i],$$

where A is a 1D array with  $(NX \times NY \times NZ)$  elements and B a 3D matrix of dimension  $(NX \times NY \times NZ)$ . If the size of the domain is  $(NX \times NY \times NZ)$ , then the index translation from the thread ID (in a 2D CUDA grid) to a 1D array element index in global memory is given by:

(c) CUDA block decomposition (d) CUDA thread indices (blockIdx.x, blockIdx.y) (threadIdx.x, threadIdx.y)

Figure 3.6: Example of index logic to map a 2D CUDA block decomposition onto a 3D domain. The 3D domain (a) is represented in a 2D-way (b). A 2D CUDA grid is then mapped onto the 2D domain (c). (d) represents the thread indices associated to the CUDA block decomposition.

$I = gridDim.x \times blockDim.x \times blockDim.y \times blockIdx.y$

- +  $threadIdx.y \times gridDim.x \times blockDim.x$

- +  $blockIdx.x \times blockDim.x + threadIdx.x$

where I is the index used to access the global memory (1D array).

(blockDim.x, blockDim.y) represents the dimensions of a single CUDA block and (blockIdx.x, blockIdx.y) the ID (2D coordinates) of the block to which the current thread belongs to. The ID of the thread inside the block is given by (threadIdx.x, threadIdx.y). Using the example given in Figure 3.6 and Eq. 3.1, thread (0,1) from block (0,3) updates the 1D array element at the index *I* defined by:

$$I = 4 \times 2 \times 2 \times 3$$

$$+ 1 \times 4 \times 2$$

$$+ 0 \times 2 + 0$$

$$I = 56$$

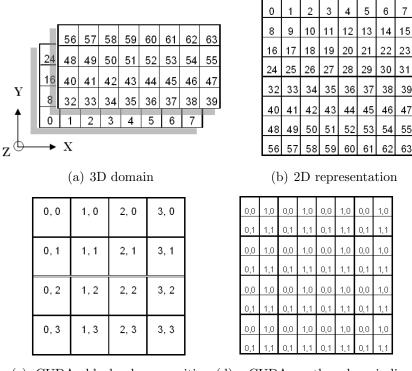

Using this index logic, each thread becomes responsible for one computational node of the domain. As discussed in Section 3.2.4, in some cases it might be interesting to have one thread responsible for multiple grid cells. In Figure 3.7, a 2D CUDA grid of  $4 \times 4$  blocks and  $2 \times 2$  threads per block is mapped onto the 3D domain. Each thread block is responsible for 2 subdomains aligned in the z-direction. For this approach, the size of the CUDA grid is defined by:

$$(gridDim.x, gridDim.y) = (GRID\_SIZE\_X, GRID\_SIZE\_Y \times SIZE\_Z), (3.1)$$

where GRID\_SIZE\_X is the number of blocks in the x-direction, GRID\_SIZE\_Y is the number of blocks in the y-direction necessary to represent a slice of the domain in the XY plane, and SIZE\_Z is the number of levels in the z-direction on which a single block work. The index of the first element on which a given thread should work is defined by:

|       | $\int$      | 0   | 1   | 2       | 3   | 4   | 5   | 6   | 7   | 0, 0                           | 1, 0    | 2, 0  |

|-------|-------------|-----|-----|---------|-----|-----|-----|-----|-----|--------------------------------|---------|-------|

| z = 0 |             | 8   | 9   | 10      | 11  | 12  | 13  | 14  | 15  |                                |         |       |

|       |             | 16  | 17  | 18      | 19  | 20  | 21  | 22  | 23  | 0, 1                           | 1, 1    | 2, 1  |

|       | L           | 24  | 25  | 26      | 27  | 28  | 29  | 30  | 31  |                                |         |       |

| z = 1 | $\int$      | 32  | 33  | 34      | 35  | 36  | 37  | 38  | 39  | 0,0                            | 1, 0    | 2,0   |

|       |             | 40  | 41  | 42      | 43  | 44  | 45  | 46  | 47  |                                |         |       |

| 2 1   |             | 48  | 49  | 50      | 51  | 52  | 53  | 54  | 55  | 0, 1                           | 1, 1    | 2, 1  |

|       | L           | 56  | 57  | 58      | 59  | 60  | 61  | 62  | 63  |                                |         |       |

| z = 2 | $\int$      | 64  | 65  | 66      | 67  | 68  | 69  | 70  | 71  | 0, 2                           | 1, 2    | 2, 2  |

|       |             | 72  | 73  | 74      | 75  | 76  | 77  | 78  | 79  |                                |         |       |

|       |             | 80  | 81  | 82      | 83  | 84  | 85  | 86  | 87  | 0, 3                           | 1, 3    | 2, 3  |

|       | L           | 88  | 89  | 90      | 91  | 92  | 93  | 94  | 95  |                                |         |       |

| z = 3 | $\int$      | 96  | 97  | 98      | 99  | 100 | 101 | 102 | 103 | 0,2                            | 1, 2    | 2,2   |

|       |             | 104 | 105 | 106     | 107 | 108 | 109 | 110 | 111 |                                |         |       |

|       |             | 112 | 113 | 114     | 115 | 116 | 117 | 118 | 119 | 0,3                            | 1, 3    | 2,3   |

|       | L           | 120 | 121 | 122     | 123 | 124 | 125 | 126 | 127 |                                |         |       |

| (2)   | <u>о</u> р. |     |     | + - + : |     |     |     |     |     | $(\mathbf{b}) \mathbf{M}_{ar}$ | ning of | the ( |

(a) 2D representation of the memory

(b) Mapping of the CUDA grid

Figure 3.7: Final index logic to map the CUDA block decomposition onto a 3D domain. (a) An  $8 \times 4 \times 4$  domain is stored as a 1D array in memory. (b) A 2D CUDA grid is mapped onto the 1D array in memory, each  $2 \times 2$  thread block working on two levels in the z-direction.

| $I_{temp}$ | = | $gridDim.x \times blockDim.x \times blockDim.y$                                                |

|------------|---|------------------------------------------------------------------------------------------------|

|            | × | $(blockIdx.y\%GRID\_SIZE\_Y)$                                                                  |

|            | + | $threadIdx.y \times gridDim.x \times blockDim.x$                                               |

|            | + | $blockIdx.x \times blockDim.x + threadIdx.x$                                                   |

| Ι          | = | $I_{temp} + (NX \times NY \times SIZE_Z) \times \lfloor blockIdx.y/GRID\_SIZE_Y \rfloor (3.2)$ |

In the example given in Figure 3.7, the size of the CUDA grid defined by Eq. 3.1 becomes:

$$(gridDim.x, gridDim.y) = (4, 2 \times 2) = (4, 4)$$

3, 0

3, 1

3,0

3,1

3, 2

3, 3

3,2

3,3

In this configuration the thread (1,0) from the block (1,2) would start working with the element located at the index I calculated as follows:

$$I_{temp} = (4 \times 2 \times 2 \times (2\%2)) + (0 \times 4 \times 2) + (1 \times 2) + 1$$

$$I = I_{temp} + (8 \times 4 \times 2) \times \lfloor 2/2 \rfloor$$

$$I = 67$$

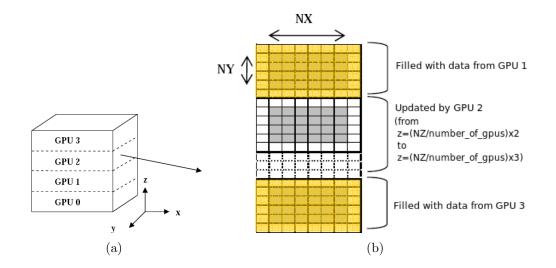

Thread (1,0) from block (1,2) is then represente the array elements at the indices 67 and  $(67 + NX \times NY) = (67 + 8 \times 4) = 99$ . The code for the index logic is given in Appendix C.2.